三星宣布3nm成功流片!

三星距离台积电又近了一步!据外媒最新报道,三星宣布3nm制程技术已经正式流片。

报道显示,三星3nm制程采用的是GAA架构,从性能角度来说要胜于台积电3nm采用的FinFET架构。但由于采用的是GAA架构而非FinFET架构,因此三星需要新的设计和认证工具,从而采用了新思科技的Fusion Design Platform,目的在于加速为GAA架构的生产流程提供高度优化的参考方法。

据三星介绍,3nm与5nm制造工艺相比,3nm GAA技术的逻辑面积效率提高了35%以上,功耗降低了50%,性能提高了约30%。三星代工设计技术团队副总裁Sangyun Kim表示:“三星代工是推动下一阶段行业创新的核心,我们不断进行基于工艺技术的发展,以满足专业和广泛市场应用不断增长的需求。我们最新的、先进的3nm GAA工艺受益于我们与新思科技的广泛合作,Fusion Design Platform加速准备以有效实现3nm工艺的承诺,证明了这些关键联盟的重要性和好处。”

当然,引起业内广泛关注的不止是3nm制程带来的性能提升,还有三星在GAA架构上的大胆尝试。为什么三星会采用GAA架构,而不跟随台积电走FinFET的道路呢?

众所周知,半导体工艺制程在进入32nm以下的节点后每一步都充满艰辛,科学家和工程师们在过去的数年间也发明了各种各样的增强技术来对抗继续微缩尺度所带来的不确定性,但量子效应始终是拦在先进制程路上的拦路虎。如今已经进入7nm、5nm时代,如果要进一步向更小尺寸的工艺节点前行的话,又有新的麻烦。

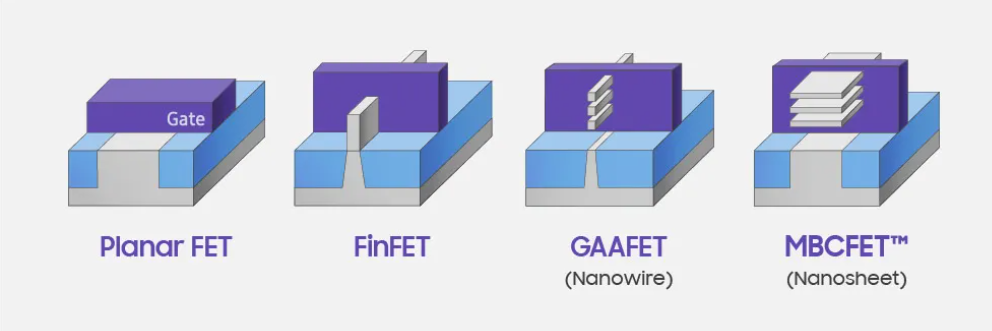

现有半导体制造的主流工艺大都采用“鳍片晶体管”也就是FinFET技术进行,它成功地延续了22nm以下数代半导体工艺的发展。从技术发展角度来看,平面晶体管在尺寸缩小至22nm后,漏电流控制将变得很困难。这是因为“势垒隧道效应”导致了电流泄露。

所谓“势垒隧道效应”是指虽然源极和漏极被绝缘的物体隔开无法导通,但是在绝缘层越来越薄之后,源极和漏极之间的距离也越来越近,最终两者过于靠近,稍微施加电压就会使得电子以概率的方式穿透绝缘层到达另外一端,这就带来了漏电流和功耗问题。解决问题的方法就是FinFET,也就是将漏极和源极“立起来”,栅极再垂直构造,形成了经典的FinFET“鳍片”结构。这种经典的结构不但在很大程度上增厚了绝缘层、解决了平面晶体管的隧道效应,还为栅极带来了更多有效的接触面,使得电流阻碍降低,发热也随之下降。

从22nm时代开始,FinFET就成为各家厂商用于缩小晶体管尺寸的法宝。不过再好的法宝也有失效的一天。随着晶体管尺度向5nm甚至3nm迈进,FinFET本身的尺寸已经缩小至极限后,无论是鳍片距离、短沟道效应、还是漏电和材料极限也使得晶体管制造变得岌岌可危,甚至物理结构都无法完成。

一个典型的例子就是,在5nm之后,FinFET几乎已经达到了物理极限,其不断拉高的深度和宽度之比(为了避免短沟道效应,鳍片的宽度应该小于栅极长度的0.7倍),将使得鳍片难以在本身材料内部应力的作用下维持直立形态,尤其是在能量更高的EUV制程导入之后,这样的状况会更为严重,甚至光子在如此小的尺度下将呈现量子效应从而带来大量的曝光噪音,严重影响了产品的质量和性能。另外,栅极距过小将带来不可控的情况。

以英特尔工艺为例,14nm制程下,栅极距是70nm,10nm工艺下栅极距是54nm。栅极距随着工艺演进而不断缩小,IMEC的模拟显示,栅极距在现有FinFET技术下的极限是42nm,制程达到5nm甚至3nm时,栅极距还会缩小,当小于42nm时,人们引以为傲的FinFET将无法继续使用下去。

-

Tesvolt和三星推出新的高压存储系统

2021-06-22 -

除中国市场外 全球登记的电动车动力电池共36GWh、同比增长103.7%

2021-06-18 -

美国发布动力电池宏伟蓝图 日韩电池玩家大举涌入

2021-06-17 -

三星将推出新款手机,但似乎有点眼熟?

2021-06-16 -

投资2000亿韩元!三星SDI再次扩产!

2021-06-16 -

三星竟然给竞争对手提供折叠屏,原因在这!

2021-06-11 -

大兴安岭供电公司:缓解结构性缺员 推进营配调贯通

2021-06-11 -

1~4月动力电池市场分析丨借力爆款车型 磷酸铁锂电池占得半壁江山

2021-06-09 -

折叠手机霸主三星Fold3将首发屏下镜头!

2021-06-08 -

CATL与长城签订战略协议 亿纬/孚能/欣旺达电池订单接到手软

2021-06-08 -

基于ZNS技术,三星推出新一代固态硬盘!

2021-06-03 -

其实你和三胎之间,也许就差这一支神奇的股票!

2021-06-02 -

美国要新建6-7家半导体厂 台积电、三星、英特尔分摊任务?!

2021-05-28