时序电路为什么综合成了latch

有群友提问,下面的代码为什么在DC里可以综合成DFF,而在FPGA上却综合成了latch。

always@(posedge clk, negedge rstn, negedge setn) if(!rstn) a <= 1'b0; else if(!setn) a <= 1'b1; else a <= a;

我们可以看到这段代码有两个特别之处:

同时有异步复位和异步置位

除了复位和置位,数据要保持

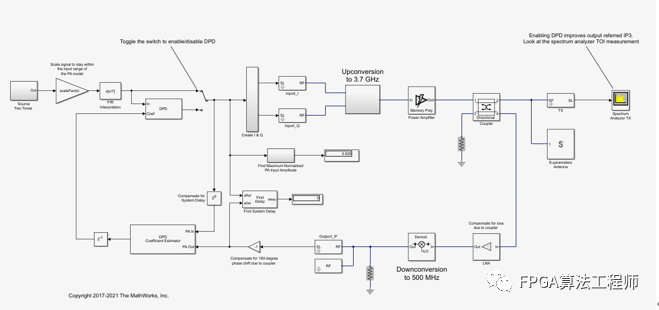

我们可以画出这段代码的逻辑图,如下图。这图也就是DC综合出来的结果。

那在FPGA上为什么会变成latch呢?有人说FPGA平台没有latch,但quartus里确实报了生成latch的warning。我们来试着把电路等价变换,先把setn端简化掉:

我们看到上图左边dff的逻辑,当rstn==0时,dff输出0,否则就保持。这不就是latch的逻辑吗?整理出下图:

由此可见FPGA平台综合成latch也是有可能的。

后来让群友直接看看FPGA平台综合出来的电路图,看看究竟是什么样的电路。群友回复如下:

哎,真是神奇!时钟都优化没了,直接用了一个带复位和置位的latch。看了这个电路的逻辑,确实与一开头的RTL等价的,并且还不需要数据loop了,挺简洁的。

所以得出结论,FPGA平台之所以与DC有差异,只是综合策略或者说是综合引擎优化算法的问题。综合结果都是可以用的。

原文标题:时序电路为什么综合成了latch

郑重声明:文章仅代表原作者观点,不代表本站立场;如有侵权、违规,可直接反馈本站,我们将会作修改或删除处理。

相关阅读

猜你喜欢

-

切尔诺贝利的树木构成了巨大的环境威胁

2022-03-22 -

从对俄罗斯天然气的依赖转向了美国,这场欧洲能源危机,美国又成了最大的受益者?

2022-03-15 -

2021年《政府工作报告》量化指标任务完成了!北方地区清洁取暖率达到73.6%!

2022-03-03 -

阿里巴巴成立新公司!经营范围包括集成电路

2022-02-25 -

新能源车企争相IPO,港股为何成了“香饽饽”?

2022-02-25 -

加拿大的LNG梦想变成了噩梦

2022-02-23 -

天然气卡特尔形成了吗?

2022-02-18 -

教育部公布 “双一流”建设名单 复旦拿下唯一集成电路一级学科

2022-02-14 -

京东方新成立一家科技公司!经营范围包含集成电路设计

2022-02-11 -

AMD350亿美元收购赛灵思,成了!

2022-02-11 -

国家大基金入局印刷电路板龙头深南电路!

2022-02-10 -

一文看尽集成电路产业的“十四五”规划

2022-02-08 -

欧佩克的任务“完成了”吗?

2022-02-05 -

如果宁德时代把换电做成了,将会有怎样的结果?

2022-01-27 -

锂电材料疯狂扩产!锂电池铜箔产线成了印钞机?

2022-01-21